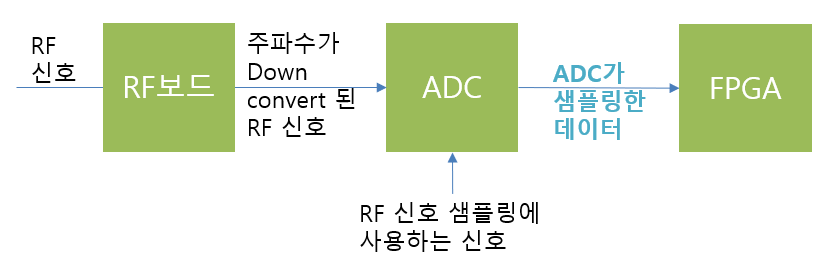

아날로그 신호 s(t)가 있다. 이것을 주파수 domain에서 표현하면, s(t)는 다음과 같이 f0에 중심을 두고 일정한 대역폭을 가지고 있는 신호라고 보자. 아날로그 신호 s(t)를 Fourier Transform을 이용하여 주파수 domain에 표현하면 다음과 같이 표현된다. cosωt가 + 주파수의 복소신호와 –주파수의 복소 신호의 합으로 표현된 것 과 같이 신호 s(t) 또한 +f0주파수와 –f0주파수에 나뉘어서 표현된다. 아날로그 신호 s(t)를 fs 주파수로 샘플링한다. 샘플링 된 이산 신호를 DFT(Discrete Fourier Transform)에 넣어 주파수 domain에 표현한다. 다음과 같이 원래신호뿐만 아니라, 원래 신호의 aliasing 신호들이 반복적으로 fs 간격마다 표현된다..