본 내용과 그림은 TI 사의 JESD204B 설명자료를 참고하였습니다

JESD 204B의 데이터 전송과정이 어떻게 진행되는지를 다음 그림에서 확인할 수 있다.

JESD204 TX 모듈과 RX 모듈, 클럭 제너레이터로 구성되어 있다.

TX 모듈과 RX 모듈 모두 Transport layer, Link layer, Physical layer로 구성되어 있다는 점은 같으며, 통과하는 layer의 순서가 다르다.

JESD204를 지원하는 ADC가 JESD204 TX 모듈을 가지고 있으며

ADC가 보낸 데이터를 수신해야하는 FPGA가 JESD204 RX 모듈을 가지고 있다.

JESD204 부분을 구현하면서 알아야할 부분이 Physical layer, Link layer, Transport layer이다.

이 글에서는

JESD204 TX 모듈에서는 Transport layer -> Link layer -> Physical layer 과정을 거치며

JESD204B RX 모듈에서는 Physical layer -> Link layer -> Transport layer 과정을 수행한다.

TX 모듈과 RX 모듈의 layer들의 역할은 같으나 그 순서와 방향이 다르다. 예를 들면

TX 모듈 Transport layer가 데이터 형태를 parallel -> serial로 변경하면

RX 모듈 Transport layer는 데이터 형태를 serial -> parallel로 변경하는 역할을 한다.

JESD204 TX 모듈 관점에서 Link Layer와 Transport layer에 대해 주로 언급하도록 하겠다.

Transport layer

Transport layer의 대표적인 역할이

ADC에서 Parallel하게 나오는 데이터를 Serial 형태로 만들어주는 것이다.

Parallel하게 나오는 데이터를 Serial하게 배치하는 형식은 제조사마다 다르지만, 대략 다음 그림과 같은 형식으로 배치한다. 주요 특징으로는 ADC에서 나오는 데이터를 Octet이라는 단위(8비트씩 끊음)로 배치한다는 점이다.

JESD204 데이터 전송을 설계할 때 ADC 규격, 데이터 전송환경에 따라 M, S, K, F, L, RBD 값을 설정하며, 이 숫자의 의미에 대해 알아야 한다. JESD RX 부분을 구현할 때도 TX에서 설정한 M, S, K, F, L, RBD 값에 맞추거나 감안해야한다.

아래의 그림은 8개의 ADC로 구성된 Device의 Trasnport layer를 나타낸 것임.

M - Device를 구성하는 ADC의 샘플 개수

S - Frame에 들어가는 ADC의 샘플 개수, 아래 그림에서는 Device의 샘플 (8개의 ADC의 각각의 샘플이 모여진) 1개씩 들어가 있으므로 1임. ADC의 개수와 관련있지 않음!

F - Frame을 구성하는 octet의 개수, octet이 모여서 frame 구성

K - Multiframe을 구성하는 frame의 개수, frame이 모여서 multiframe 구성

L - Device의 JESD204 데이터 전송 Lane의 개수

RBD - JESD204 데이터 전송에 고의로 Delay를 줄 수 있는데, 그 Delay의 정도(저는 보통 0으로 해두었습니다.)

Link layer

Link layer의 3가지 역할은 다음과 같다.

- 8b/10b encoding

- Code Group Synchronization(CGS)

: JESD RX 모듈이 Frame의 시작점을 정렬할 수 있도록 함.

- Initial Lane Synchronization(ILAS)

: Data Lane들간의 동기를 맞추는 작업을 함.

- 8b/10b encoding

Transport layer에서 octet(8bit)단위로 데이터를 serialize한다고 했다. serialize된 데이터에 8b/10b 인코딩을 수행한다. 다음 그림과 같이 코드화한다. 8비트를 10비트로 늘린다는 말이다. 8b/10b 인코딩은 jesd204 뿐만 아니라 다른 고속 통신에도 사용된다.

- CGS, ILAS

JESD204의 TX 모듈이 데이터만 보내면 RX 모듈이 어디부터 데이터인지 알 수 없다. 따라서 RX 모듈이 데이터의 시작점을 알 수 있도록, TX 모듈은 데이터 시작 관련 정보를 만들어서 전달해야 한다.

이 시작관련 정보가 CGS, ILAS이다.

CGS는 JESD RX 모듈이 Frame의 시작점을 정렬할 수 있도록 함.

ILAS는 Data Lane들간의 동기를 맞출수 있도록 한다.

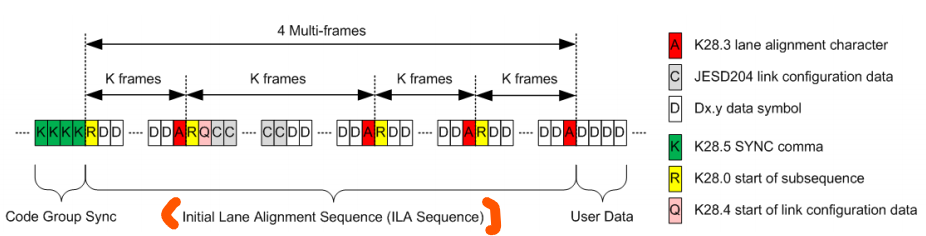

- Code Group Synchronization

위 그림은 CGS, ILAS에서 사용되는 8b/10b 코드를 나열한 것이다. CGS는 K28.5 코드(8b/10 코드표)가 사용된다.

JESD204 데이터 전송 중 CGS는 다음과 같이 수행된다.

1. RX가 SYNC pin을 Low로 하여, CGS 단계가 필요하다고 TX에게 알린다.

2. TX는 /K28.5/ sysboms(10bits/symbol)을 보낸다.

3. RX가 적어도 4개의 K28.5 심볼(8b/10b characters)을 문제 없이 받으면 SYNC pin을 High로 한다.

- 이 과정이 실패하면 ILAS 단계로 넘어가지 못하고 CGS에 머문다.

4. 3번 과정이 문제가 없으면, RX는 Frame boundry를 다음에 수신하는 non-K28.5 심볼에 align한다. 그러면 CGS 단계가 끝나고 ILAS 단계로 넘어간다.

- Initial Lane Alignment Sequence

앞선 CGS 단계에서 RX가 Frame의 시작점을 정렬했다면, ILA 단계에서는 data Lane들간의 동기를 맞추는 작업을 한다.

TX 모듈은 CGS의 심볼 다음에 multi frame을 보낸다. 이 multi frame에 ILA 단계의 내용을 넣어 보낸다.

ILA는 최소 4개의 multi frame으로 구성된다.

이 multi frame안에는 configuration parameter code(K28.3) alignment symbol code(K28.0)등 이 들어간다.

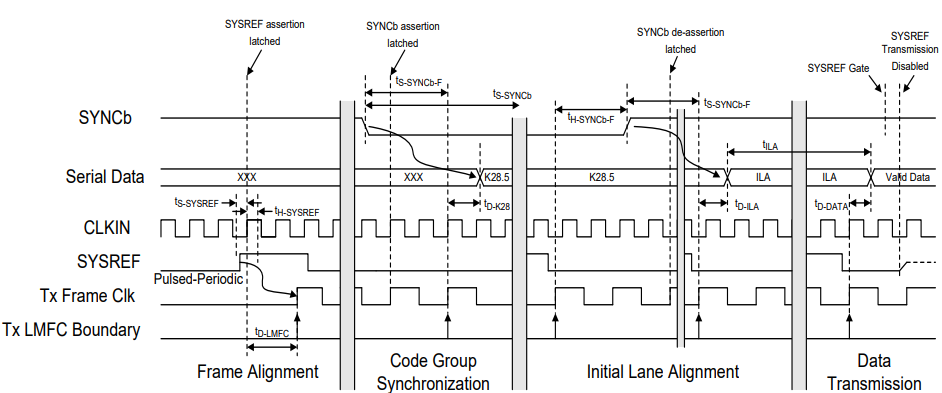

다음 그림은 위의 과정을 한꺼번에 보여주는 그림이다.

1. TX모듈은 클럭제네러이터로부터 SYSREF 신호를 받으면 Frame clock을 SYSREF 기준으로 동기화한다.

2. RX모듈로부터 ~SYNC 신호, SYNC(0)를 받으면 TX 모듈은 CGS 단계를 시작한다.

3. RX모듈로부터 SYNC(1)을 받으면 TX 모듈은 ILAS 단계를 시작하고, 그 다음 보내려했던 ADC 데이터(8b/10b 인코딩된)를 보낸다.

* 앞선 글에서 JESD204B 외부 clock을 정리하였다면, 이제는 JESD204B 모듈의 내부클럭에 대해 알아보자. 이 내부 클럭은 외부클럭을 받아 생성된 것이다.

주요 내부클럭으로

LMFC clock

• Data frame of the transport layer is aligned to the frame clock

• Frame clock period in all the TX and RX devices must be identical

Frame clock

• Multi-Frame is composed of ‘K’ Frames, Mulit frame은 K개의 Frame으로 구성한다.

• LMFC is aligned to the multi-frame boundary

• Acts as a low-frequency reference to resolve frame clock phase

ambiguity across multiple devices

• LMFC period in all TX and RX devices must be identical

Physical layer

- Physical layer는 앞선 글에서 언급했던 Transceiver로 Xilinx FPGA로 JESD204 RX 부분을 구현할 때 Xilinx FPGA의 MGT 모듈이 Transceiver의 역할을 수행함.

'FPGA - 프로세서 그리고 데이터의 이동 > JESD204' 카테고리의 다른 글

| 1. JESD204B의 시작 (0) | 2022.04.01 |

|---|---|

| JESD204B - Deterministic latency의 측정 (0) | 2021.08.27 |

| JESD204B - Total Link Latency(=Deterministic Latency)의 계산 (0) | 2021.08.27 |

| JESD204B - Deterministic latency를 조정할 수 있는 수단 (0) | 2021.08.27 |

| JESD204B - SYSREF의 주파수 설정 (0) | 2021.08.26 |