본 문서는 Analog Device사의 문서를 보고 작성하였습니다.

JESD 204B에서 언급되는 Deterministic latency는 위의 그림에서 Framer to De-framer까지의 소요시간이다. 참고로 ADC가 아날로그 신호를 디지털로 변환하는 시간은 Deterministic latency에 포함되지 않는다.

JESD204B의 subclass 1을 지원하는 칩 내부에 frame clock과 multiframe clock이 있다. 이 칩이 SYSREF 신호를 인식하면 SYSREF 신호를 기준으로 frame clock과 multiframe clock을 정렬하여 frame clock과 multiframe clock의 위상이 일치한다.

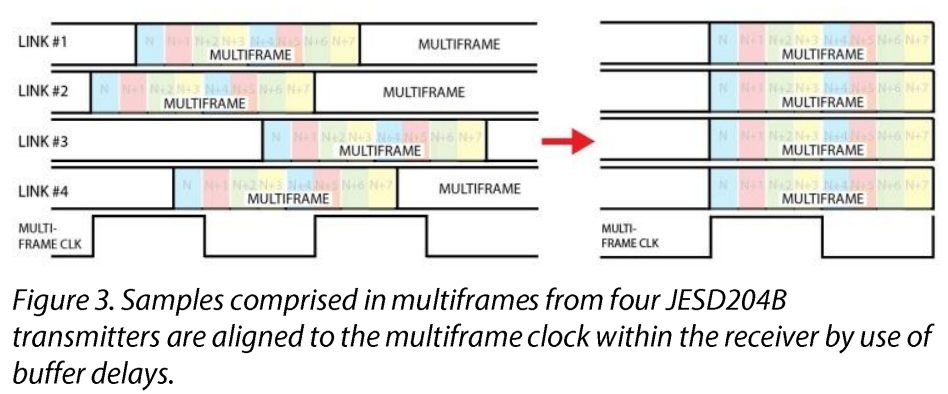

ADC가 샘플링한 데이터들이 ADC 내부 JESD204B송신모듈을 거쳐, 데이터 lane(아래그림에서 link)에 전송된다. 그리고 이것이 FPGA 내부 JESD204B 수신모듈에 도착한다. 각 lane들마다 데이터의 도착시간이 다르다. 이 말은 각 lane마다의 determinsitc latency가 다르다는 말이다. 각 lane에 도착한 데이터들의 위상을 똑같이 만들어야 한다.

수신모듈의 multiframe clock의 edge와 각 lane에 도착한 특정데이터(ILAS 단계에 사용한 character)사이의 delay를 비교하여 각 lane의 deterministic latency를 구할 수 있다. 도착한 데이터들은 수신모듈의 버퍼에 저장된 다음 수신 모듈의 Multiframe의 위상에 맞추어 정렬할 수 있다.

참고로 수신모듈 또한 SYSREF 신호를 받아 frame clock과 multiframe clock이 정렬이 된 상태이다.

여기서 꼭 지켜야할 점은 각 lane의 deterministic latency는 multiframe clock의 주기보다 짧도록 해야 한다. 문서에 이렇게 적혀 있다. -> The deterministic latency for each link must be shorter than the duration of a multiframe clock period. 아래 그림에서, 초록색 지점에서 TX가 송신하면 RX가 데이터를 인식할 때까지 시간이 주황색으로 칠해진 부분 이내이어야 한다는 말이다.

LMFC의 주기를 구하는 방법을 예로 들면 다음과 같다.

• Example: Serial Rate (SR)=10 Gb/s, F=2, K=32. What is LMFC period?

• TLMFC = 10*F*K/SR = 10*2*32/10e9 = 64ns (32 frame clock cycles)

위 과정을 한번에 정리한 그림이 다음 그림이다. TI사에서 정리한 자료인데 이해할 때 좋은 것 같다.

'FPGA - 프로세서 그리고 데이터의 이동 > JESD204' 카테고리의 다른 글

| JESD204B - Deterministic latency를 조정할 수 있는 수단 (0) | 2021.08.27 |

|---|---|

| JESD204B - SYSREF의 주파수 설정 (0) | 2021.08.26 |

| 3.1 JESD204 구현에 필요한 하드웨어 (0) | 2021.07.06 |

| 2. JESD204 데이터 전송 속도 (0) | 2021.06.07 |

| 3.2 JESD204 구현에 필요한 하드웨어 - SYSREF, SYNC (0) | 2021.06.04 |