ADC의 경계는 어디인가?!

ADC의 입력부는 아날로그 회로부에 연결되고 ADC의 출력부는 디지털회로부에 연결된다. 이렇게 ADC 칩은 디지털회로부와 아날로그 회로부의 경계에 걸쳐있는 부품이다.

ADC의 데이터시트를 보면 보통 2개의 Ground가 있다.

Digital Gnd, Analog Gnd가 있다. 음?? 어떻게 해야할까?

Analog Gnd는 ADC가 들어가는 보드의 아날로그 회로부 Gnd에 연결하고, Digital Gnd는 ADC가 들어갈 회로의 디지털 회로부 Gnd에 연결하면 되는 것인가??

결론적으로 말하면 ADC의 Digital Gnd, Analog Gnd 둘 다 아날로그 회로부의 Gnd에 연결하는 것이 맞다.

그이유를 살펴보자. 본 글의 내용은 TI 사의 ADC GND에 대한 정리자료를 읽고 정리한 것입니다.

우선 용어 정의를 하겠다.

ADC 운용 보드 : ADC가 장착된 보드

ADC 내부를 보면, 아날로그 부분과 디지털 부분이 존재하며 각각의 Ground인 AGND, DGND가 있다. 그리고 두 부분 사이에 기생 커패시턴스가 존재한다.

ADC가 동작하는 동안, 디지털부분에 Ground noise가 발생한다. 이 noise[X}가 기생커패시턴스를 통해 아날로그 부분에 영향을 주기도 합니다. 이 영향을 막기 위해서 AGND와 DGND 사이의 임피던스를 줄여야 합니다.

임피던스를 줄이기 위해서 Chip의 AGND와 DGND를 ADC 운용 보드의 아날로그 회로(-> ADC의 아날로그 부분이 아니다.!! 헷갈리지 말자)의 GND에 연결하는 것이 좋다.

AGND와 DGND를 분리한답시고, DGND를 ADC 운용 보드의 디지털 회로 GND에 연결했다간, noise[X}를 오히려 크게 할 수 있다.

● 이제 다시 ADC GND에 관련한 논란(?)을 정리한다.

1. ADC 칩의 데이터 시트를 보면 AGND, DGND가 있다. 이말인 즉슨 DGND를 ADC 운용 보드의 디지털회로부 GND에 연결하고, AGND를 ADC 운용 보드의 아날로그회로부 GND에 연결하란 말인가?

->> 아니다! ADC 칩의 AGND, DGND 둘다 ADC 운용보드의 아날로그 회로부 GND에 연결하란 말이다.

2. 그렇다면 DGND는 무엇이며, 왜 헷갈리게 DGND라고 하는가?? ADC 칩 내부에는 아날로그 부분과 디지털 부분이 있다. AGND는 아날로그 부분의 GND를 DGND는 디지털 부분의 GND를 의미한다.

ADC의 데이터시트에서는 ADC의 GND를 위와 같이 연결하는 것을 권장한다.

3. 왜 ADC의 GND를 AGND, DGND로 나누는가??

ADC를 패키징하여 칩으로 만든다. 이 때 ADC 회로부를 패키지의 외부 PIN과 연결할 때 lead(그냥 전기가 통하는 선)를 사용한다. 이 Lead는 L성분을 가지고 있어서 고주파수에서 High 임피던스를 가진다.

ADC의 디지털 부분에 고주파수 신호의 전류가 흐르는 경우가 있다. 이 경우 lead 사이에 전압이 발생하고 이것이 ADC의 아날로그 부분의 동작에 안 좋은 영향을 줄 수 있다.

->> 만약 lead 임피던스가 작을 경우, 굳이 위와 같이 ADC의 GND를 AGND, DGND로 나눌 필요가 없다.

● 이제부터는 ADC 운용보드에서 ADC가 외부의 노이즈 영향을 덜 받는 방법에 대해 몇가지 정리해보았다.

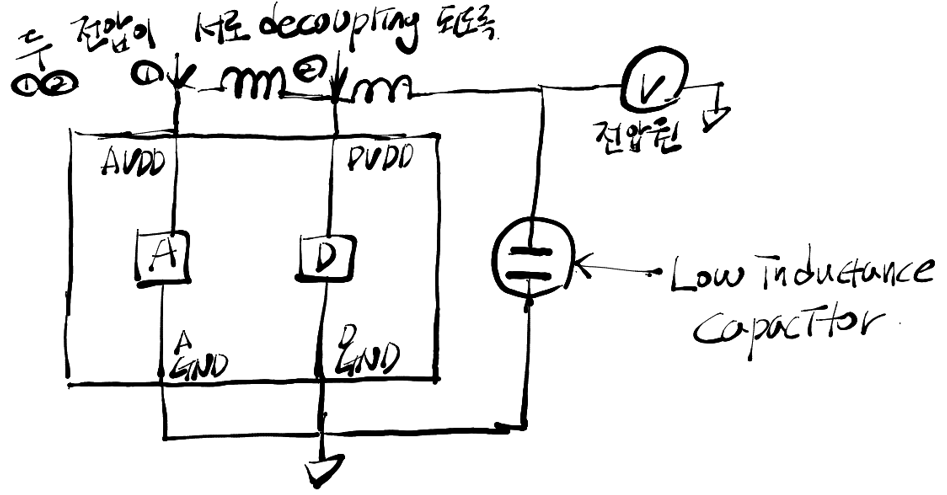

1. Supply Decoupling

Coupling이란 다른 부분의 전압(또는 신호)이 본래 있으면 안되는 전압에 엉겨 붙어서 짬뽕이 되는 것을 의미한다. 이러한 커플링을 막기 위해 위와 같이 2가지를 조치한다.

1-1 앞서 언급한 lead inductance를 낮추기 위해 Low inductance capacitor를 달아준다.

1-2 ADC의 전압 pin인 AVDD, DVDD 사이에 커플링이 발생하지 않도록 decoupling한다. (예를 들면 위와 같이 L을 달아준다.)

2. Ground Return Current

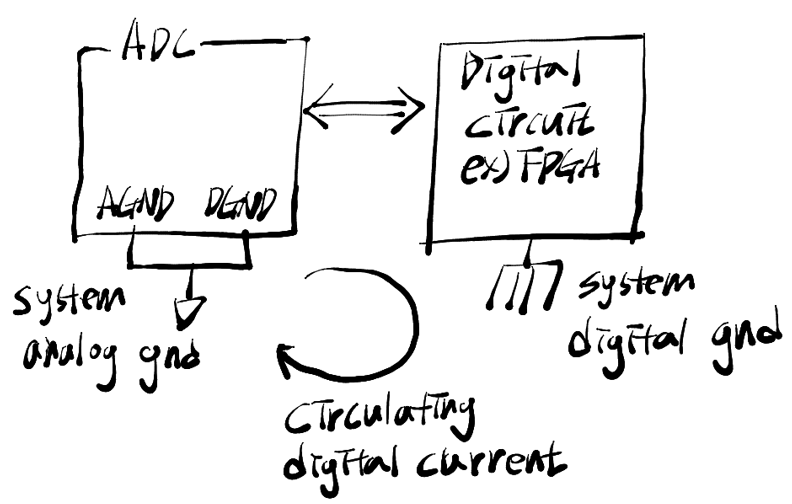

다음과 같이 ADC와 FPGA가 연결되어 있다. FPGA가 ADC를 제어할 때, 제어 신호로 인해, 또는 데이터 이동으로 인해 발생하는 전류를 GND를 통해 서로 공유한다. 이런 전류를 Ground Return Current라한다. 어쩔수 없이 이런 종류의 전류가 흐를 수 밖에 없다. FPGA와 ADC사이의 커플링 설계가 잘되어 있어서 이 전류 이외의 다른 종류의 전류가 흐르지 않는 것만해도 다행일지라도 암튼 이런 종류의 전류량이 최소가 되도록 해야 한다.

ADC에 데이터를 전송하는 버스가 연결되어, ADC로 Ground Return Current가 흐르게 되면, ADC에 노이즈를 발생시킬 수 있다.

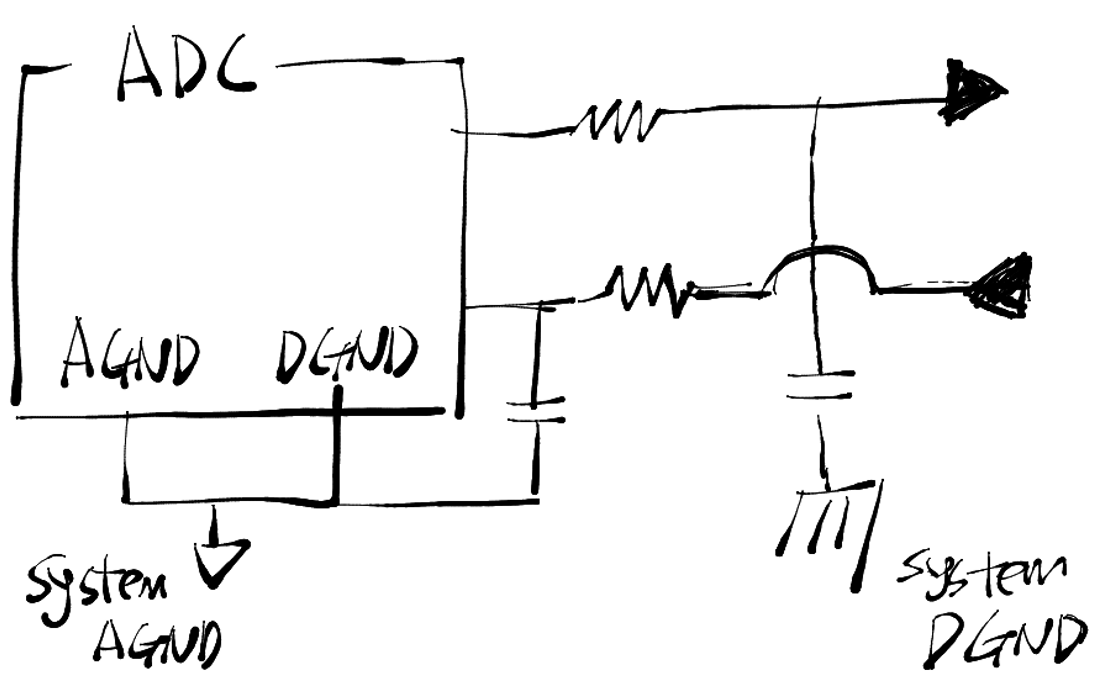

그래서 다음과 같이 중간에 buffer를 달아서 강한 Ground Return Current가 ADC에 흐르지 않도록 한다.

3. Slow Down

ADC의 데이터 라인이 고속 통신을 하게 되면, 1과 0을 왔다 갔다하는 속도가 매우 빠르다(Fast Edge). Fast edge로 인해 노이즈가 발생할 수 있다. Fast Edge를 누그러뜨리기 위해 RC 회로를 달아준다.

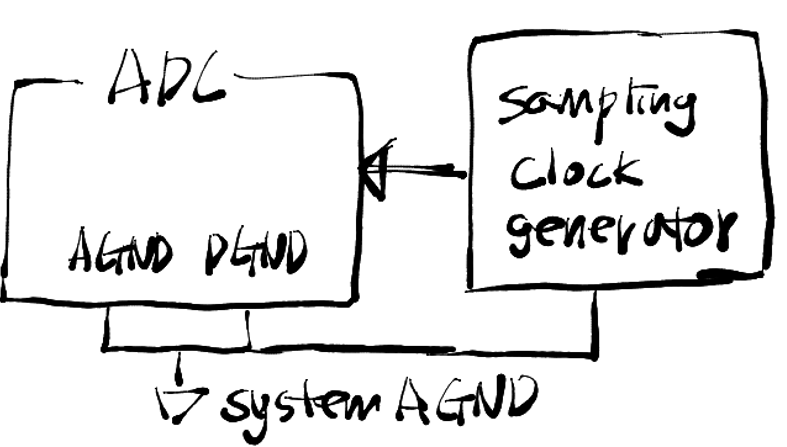

4. Sampling clocks

ADC에 Sampling clock을 공급하는 클럭제너레이터의 GND는 ADC 운용보드의 아날로그 부분의 GND에 연결한다.

5. AGND와 DGND를 분리하는 경우도 있다?

ADC 내부 컴퓨터의 연상량이 매우 높아서 디지털 부분이 발생하는 전류가 너무 큰 경우 ADC의 AGND와 DGND를 분리하기도 한다.

마이크로 컨트롤러를 내부에 포함한 ADC의 경우 마이크로 컨트롤러의 발생 전류가 작다면 AGND와 DGND를 같이 ADC운용보드 아날로그회로부 GND에 연결한다.

하지만 계산량이 많이 DSP를 내부에 포함한 ADC의 경우, DSP가 발생하는 전류가 클 경우 AGND와 DGND를 분리하기도 한다. (아마 이런 경우를 접할 일이 있을지 모르겠다)

● 전류의 흐름이 어떻게 되는지 보라

아날로그 회로에 영향을 주는 전류가 디지털 회로의 AC 신호(데이터 이동, 제어 신호에 의해 발생하는 고주파신호)인가? 아니면 DC 신호(전원)에 의한 것인지 파악하자

DC or Low frequency 신호의 전류가 흐르는 경로와 AC 신호에 의한 전류가 흐르는 경로가 다르므로, 이 두가지를 같이 고려해야 한다.

디지털 회로부와 아날로그 회로부의 영향을 서로 최소화하기 위해 PCB에 cut을 하기도 하지만, 전류 흐름을 잘 고려해야 한다.

DC 신호의 경우 Ground Return Current는 전원과 전원의 Ground사이의 최단 경로에 위치하며, AC 신호(고속 데이터, 제어신호)의 Ground Return Current는 신호선을 중심으로 분포하고 있다.

● Decouping 커패시터를 Chip에 가깝게 다는이유

decoupling을 위해 달아주는 커패시터를 Chip에 가깝게 달아주는 이유는 전원보다 빠르게 전류, 전압을 공급할 수 있기 때문이다. 칩의 전원 pin에 급격한 전압 변화가 생겨도, 칩에 가깝게 달려 있는 커패시터가 이러한 급격한 변화를 막아준다.

'ADC' 카테고리의 다른 글

| ADC의 출력 데이터라인과 출력 클럭의 PCB line 라우팅 조건 (2) | 2023.03.31 |

|---|---|

| ADC 데이터의 검증사항 (0) | 2022.07.26 |

| 아날로그 신호를 디지털신호로 바꾼다는 것 -3 (0) | 2021.12.19 |

| 아날로그 신호를 디지털 신호로 바꾼다는 것 -1 (0) | 2021.12.19 |

| 아날로그신호를 디지털신호로 바꾼다는 것 - 2 (0) | 2021.12.16 |