본 글은 ARM coretex A72 코어를 가지고 있는 프로세서의 메모리 맵에 대한 글이다.

보통 메모리 맵이라는 단어를 보면, 나는 프로세서에 연결된 SDRAM 메모리의 맵 ?, 메모리의 주소를 떠올랐다.

하지만 프로세서는 SDRAM 뿐만 아니라, GPIO, PCIe, 메모리 컨트롤러, ROM 등 여러가지 모듈과 연결 될 수 있다.

프로세서 내부에는 다음과 같은 모듈들이 서로 연결되어 있다.

프로세서는 내부 모듈 뿐만 아니라 프로세서와 외부적으로 연결되는 모듈 또한 제어할 수 있어야 한다.

이를 위해 모듈에 대한 설정 또는 제어를 위해, 프로세서는 주소표를 가지고 있다.

프로세서 내부 메모리에 모듈 또는 기능 별로 주소가 배정되어 있다.

이 주소표가 프로세서의 메모리 맵이다.

다음 그림은 ARM coretex A72 코어를 가지고 있는 프로세서 데이터 시트에 적혀있는 메모리 맵이다.

주소표 중 주목할 주소는

1. CCSR (Internal Configuration, Control, and status register)

2. DCSR(Internal Configuration, Control, and status register)

3. External memory, I/O, configuration address spaces of the PCI Express links

이다.

프로세서는 physical address(real)만 이용하여 모듈을 제어하는 것이 아니다.

Logical address, Virtual address라는 개념을 이용하여 모듈을 제어 한다.

cortex A72 코어 내부에는 MMU(Memory Management Unit)이 있다.

MMU는 logical address를 virtual address로 변환, 그리고 최종적으로 physical address(for local address space)로 변환하는 역할을 한다.

* local address 는 cortex A72 코어가 메모리나 I/O space를 접근할 때, 코어가 바라보는 physical address를 의미한다.

◎ DDR Remapping , 프로세서 외부에 연결된 DDR SDRAM 저장공간의 주소에 대한 접근은 어떻게 하는가?

프로세서 내부의 DDR controller다. DDR controller는 DDR 메모리에 읽고 쓰기를 수행한다.

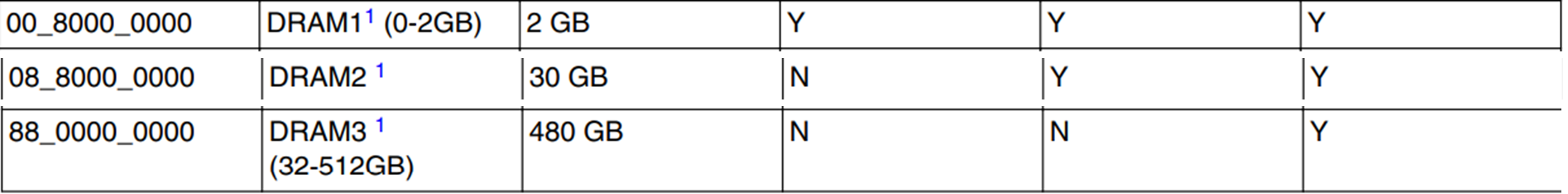

cortex A72 코어의 경우 DRAM region1,2,3의 주소는

프로세서 외부에 연결된 DDR SDRAM 메모리 주소에 다음과 같이 mapping이 된다.

Chip address가 DRAM용 주소표이며,

Remmapped DRAM 주소가 DDR SDRAM 메모리의 주소이다. 프로세서 DRAM용 주소표에서 00_8000_0000 ~ 00_FFFF_FFFF가 DDRSDRAM의 00_0000_0000 ~ 00_7FFF_FFFF와 맵핑된다.

◎ CCSR(Internal Configuration, Control, and Status Register) address map

ddr: memory-controller@1080000

{ compatible = "fsl,qoriq-memory-controller";

reg = <0x0 0x1080000 0x0 0x1000>;

interrupts = <GIC_SPI 144 IRQ_TYPE_LEVEL_HIGH>;

big-endian; };

- SPI의 CCSR 주소표, 디바이스트리

dspi: spi@2100000

{ compatible = "fsl,ls1021a-v1.0-dspi";

#address-cells = <1>;

#size-cells = <0>; reg = <0x0 0x2100000 0x0 0x10000>;

interrupts = <GIC_SPI 64 IRQ_TYPE_LEVEL_HIGH>; clock-names = "dspi"; clocks = <&clockgen 4 1>;

spi-num-chipselects = <5>; big-endian; status = "disabled"; };

- I2C의 CCSR 주소표, 디바이스트리

i2c0: i2c@2180000 {

compatible = "fsl,vf610-i2c", "fsl,ls1046a-vf610-i2c";

#address-cells = <1>; #size-cells = <0>; reg = <0x0 0x2180000 0x0 0x10000>;

interrupts = <GIC_SPI 56 IRQ_TYPE_LEVEL_HIGH>; clocks = <&clockgen 4 1>;

dmas = <&edma0 1 39>, <&edma0 1 38>; dma-names = "tx", "rx";

scl-gpios = <&gpio3 12 0>; status = "disabled"; };

i2c1: i2c@2190000 {

compatible = "fsl,vf610-i2c";

#address-cells = <1>; #size-cells = <0>; reg = <0x0 0x2190000 0x0 0x10000>;

interrupts = <GIC_SPI 57 IRQ_TYPE_LEVEL_HIGH>;clocks = <&clockgen 4 1>;

status = "disabled"; };

i2c2: i2c@21a0000 {

compatible = "fsl,vf610-i2c";#address-cells = <1>;#size-cells = <0>;

reg = <0x0 0x21a0000 0x0 0x10000>;interrupts = <GIC_SPI 58 IRQ_TYPE_LEVEL_HIGH>;

clocks = <&clockgen 4 1>;status = "disabled"; };

i2c3: i2c@21b0000 {

compatible = "fsl,vf610-i2c", "fsl,ls1046a-vf610-i2c"; #address-cells = <1>;

#size-cells = <0>; reg = <0x0 0x21b0000 0x0 0x10000>;

interrupts = <GIC_SPI 59 IRQ_TYPE_LEVEL_HIGH>;

clocks = <&clockgen 4 1>; scl-gpios = <&gpio3 12 0>; status = "disabled"; };

- GPIO의 CCSR 주소표, 디바이스트리

gpio0: gpio@2300000

{ compatible = "fsl,qoriq-gpio"; reg = <0x0 0x2300000 0x0 0x10000>; interrupts = <GIC_SPI 66 IRQ_TYPE_LEVEL_HIGH>; gpio-controller; #gpio-cells = <2>; interrupt-controller; #interrupt-cells = <2>; };

gpio1: gpio@2310000

{ compatible = "fsl,qoriq-gpio"; reg = <0x0 0x2310000 0x0 0x10000>; interrupts = <GIC_SPI 67 IRQ_TYPE_LEVEL_HIGH>; gpio-controller; #gpio-cells = <2>; interrupt-controller; #interrupt-cells = <2>; };

gpio2: gpio@2320000

{ compatible = "fsl,qoriq-gpio"; reg = <0x0 0x2320000 0x0 0x10000>; interrupts = <GIC_SPI 68 IRQ_TYPE_LEVEL_HIGH>; gpio-controller; #gpio-cells = <2>; interrupt-controller; #interrupt-cells = <2>; };

gpio3: gpio@2330000

{ compatible = "fsl,qoriq-gpio"; reg = <0x0 0x2330000 0x0 0x10000>; interrupts = <GIC_SPI 134 IRQ_TYPE_LEVEL_HIGH>; gpio-controller; #gpio-cells = <2>; interrupt-controller; #interrupt-cells = <2>; };

- DUART의 CCSR 주소표, 디바이스트리

duart0: serial@21c0500

{ compatible = "fsl,ns16550", "ns16550a"; reg = <0x00 0x21c0500 0x0 0x100>; interrupts = <GIC_SPI 54 IRQ_TYPE_LEVEL_HIGH>; clocks = <&clockgen 4 1>; status = "disabled"; };

duart1: serial@21c0600

{ compatible = "fsl,ns16550", "ns16550a"; reg = <0x00 0x21c0600 0x0 0x100>; interrupts = <GIC_SPI 54 IRQ_TYPE_LEVEL_HIGH>; clocks = <&clockgen 4 1>; status = "disabled"; };

# dmesg | grep tty

를 쳐보면

'디지털보드' 카테고리의 다른 글

| FT4232H를 이용한 SPI,I2C,Bitbang 구현 - 개요 (1) | 2024.12.26 |

|---|---|

| Device Tree 필요성, 마이크로 컨트롤러와 프로세서 사이에서의 선택 (0) | 2024.07.21 |

| 프로세서에 포함된 UART 모듈 에 대한 이해 (0) | 2023.01.11 |

| I2C 칩 연결 확인 (0) | 2022.12.23 |