PCIe, 클럭, JESD204 등 고속통신을 지원하는 칩들의 데이터 시트를 보면 신호를 LVDS(Low Voltage Differential Signaling) 형태로 보낸다고 또는 받는다고 쓰여져 있다. LVDS란 무엇인지 알고 싶어서 정리하였다.

참고한 자료는 다음과 같다.

- TI 사 LVDS 설명 자료 :

https://training.ti.com/lvds-overview?context=1135817-1139372-1135818

- Thine 사 LVDS 설명자료

https://www.thine.co.jp/ko/contents/detail/serdes-lvds.html

- Xilinx IO, GTY 데이터시트를 참고하였다.

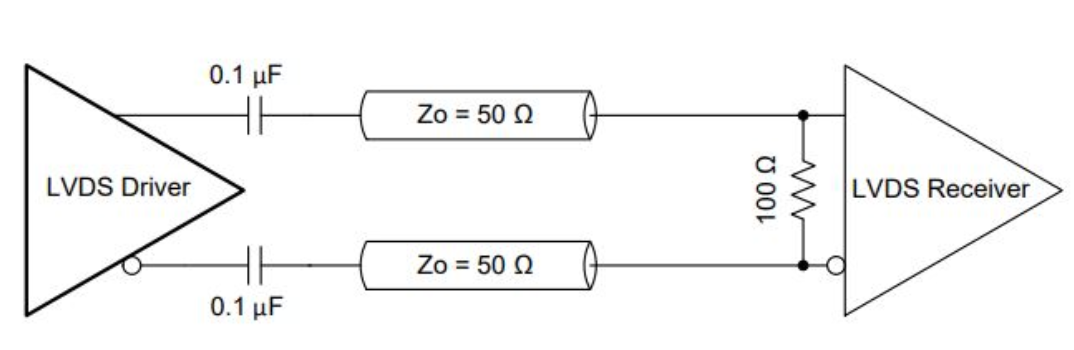

- LVDS신호 생성 및 수신을 위한 구성요소

Driver : LVDS신호를 생성

Receiver : LVDS 신호를 수신

Differentail Pair : LVDS 신호가 전송되는 신호 line (50옴 특성임피던스를 가진 전송선 2개로 구성)

100옴 Termination : Receiver 부분에 부착하는 100옴

- LVDS신호의 크기와 형태

TI의 LVDS 설명영상을 참고하였다. https://training.ti.com/lvds-overview

LVDS 신호 생성시 3.5mA가 흐른다. 그리고 이 신호는 Receiver에 도착한다. 신호가 Receiver에 도착하였더니, 100옴이 기다리고 있다. Receiver의 저항 >>>>>> 100옴 이므로, Receiver에 도착한 신호는 저항 100옴에 흐른다. 그리고 저항 양단에 3.5mA가 흐르므로, 저항 양단에는 350mV가 걸린다. Receiver는 이 350mV의 전위차 신호를 인식하게 된다.

방금 전은 Driver의 input 신호가 +인 경우였다. Driver의 input 신호가 -라면 다음 그림과 같다. 전류 흐름이 반대가 되어 수신부는 -350mV를 인식한다.

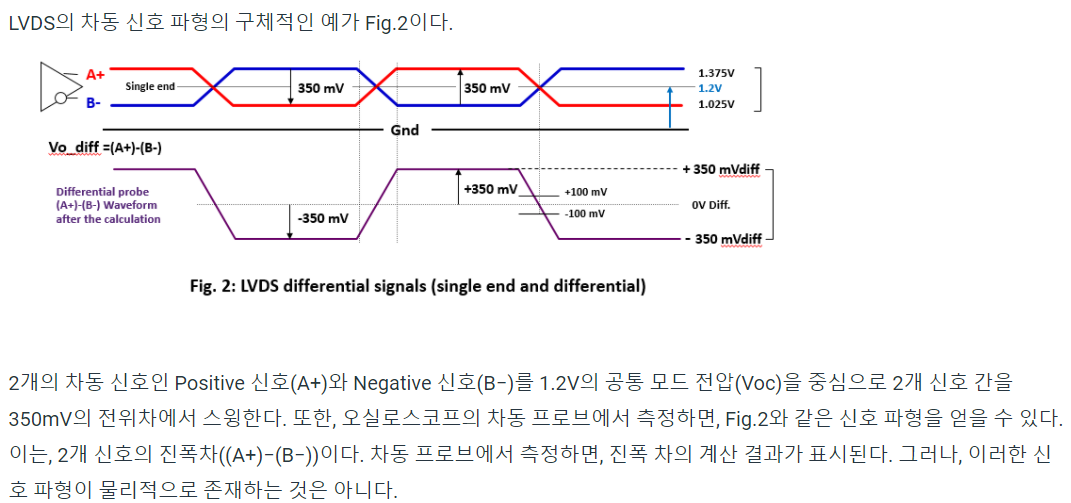

LVDS는 input 신호가 +인 경우와 -인 경우가 동시에 공존한다. 그래서 수신부는 다음자료(Thine 사 자료) 같이 differential 형태의 신호를 인식한다. 아래그림에서 (A+)가 input 신호가 +인 경우이며, (A-)가 input 신호가 -인 경우이다.

수신부가 인식하는 차동신호의 진폭이 350mV라고 언급하였는데 이 값은 nominal한 값이고, 차동신호의 진폭이 247mV~454mV까지 가능하다.

업무를 진행하면서, 차동프로브로 LVDS 신호를 측정하는 경우가 있다. 그러면 위 그림의 보랴색 파형처럼 측정이 된다.

또한 위 그림에서 보면 공통모드 전압이 있다. 이것 또한 궁금했었다. 보통 LVDS 신호를 송신할 때 350mV의 차동신호만 보내는 것이 아니라, 전압이 일정한 공통모드 전압을 중심으로 350mV의 진폭만큼 신호가 Swing하는 형태로 보낸다.

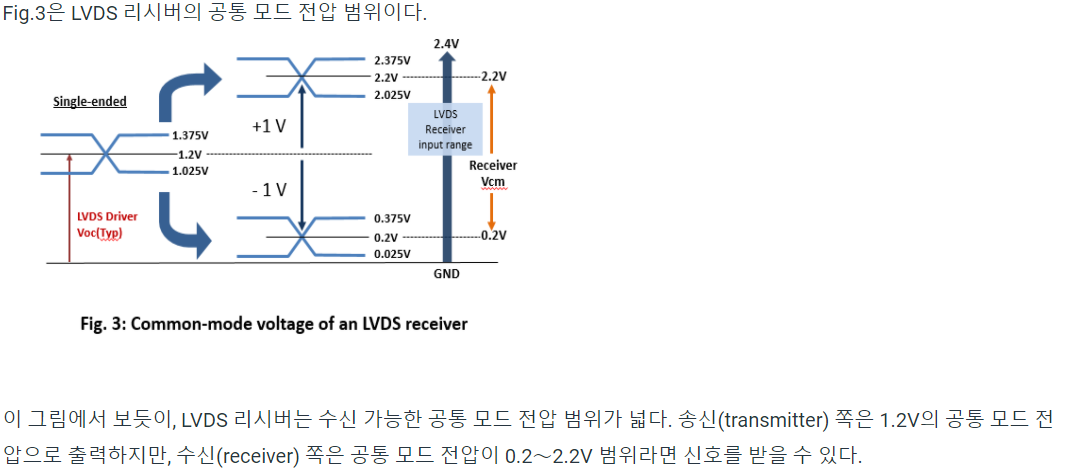

LVDS 신호의 특성으로 공통모드 전압의 범위가 넓다는 것이다. 아래 그림(Thine 사 LVDS 설명자료)과 같이 송신쪽에서 1.2V의 공통모드 전압으로 신호를 송신했지만, 모종의 이유로 신호가 전송 중에 공통모드 전압이 변경되어도 공통모드 전압이 0.2V ~ 2.2V라면 신호를 수신할 수 있다.

- LVDS신호 송수신 구조의 형태와 예시

LVDS 신호를 지원하는 chip들의 데이터시트에서 LVDS 신호를 수신할 때 어떻게 회로를 구성해라 라고 쓰여있다. 주로 다음 형태의 LVDS 신호 송수신 구조가 언급이 된다.

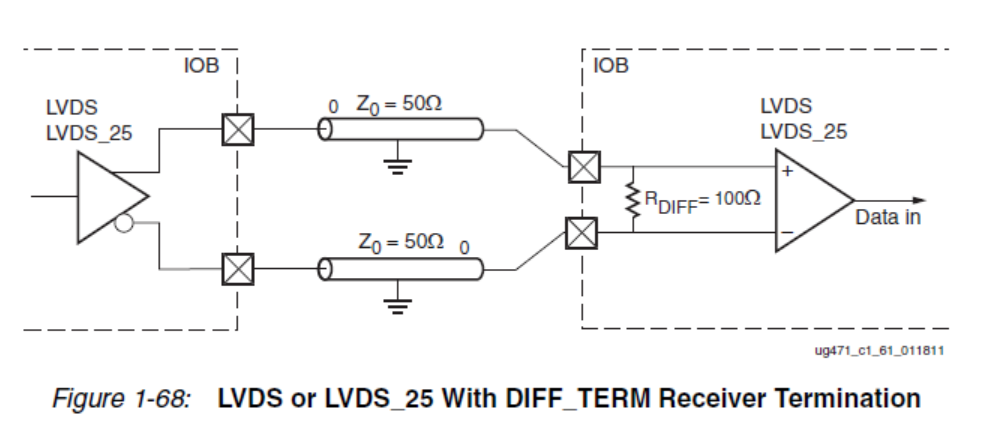

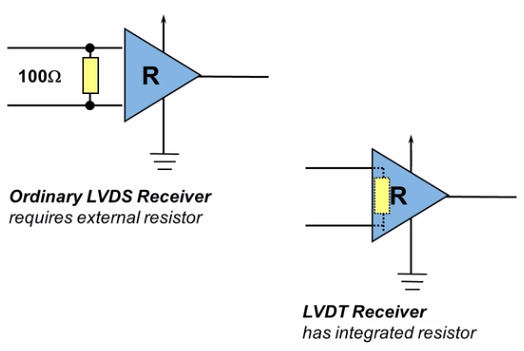

다음 예시는 Xilinx FPGA의 LVDS Driver, Receiver다. 참고로 Xilinx FPGA의 경우 LVDS Receiver 내부에 100옴을 포함하고 있어, 굳이 FPGA LVDS Receiver 외부에 100옴을 달아주지 않아도 된다. 아래 그림과 같이 말이다.

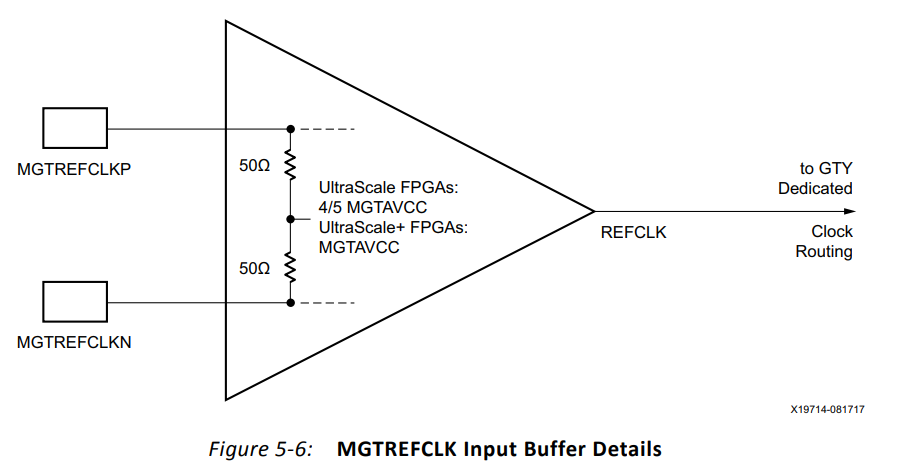

다음 예시는 LVDS 신호가 receiver에 도착하였을 때, receiver가 수신한 신호의 공통모드 전압에 대한 것이다. 아래 예시는 Xilinx사의 Ultrascale 계열 FPGA의 LVDS 수신부이다. 이 경우 공통모드 전압은 FPGA의 MGTAVCC라는 pin에 인가된 전압값으로 결정된다.

'FPGA - 프로세서 그리고 데이터의 이동' 카테고리의 다른 글

| xilinx FPGA의 Configuration 방법 (0) | 2022.12.17 |

|---|---|

| FPGA - MGT bank의 신호 지원 규격 (0) | 2021.08.24 |

| IOBUF (0) | 2021.08.04 |

| SPI 통신 (0) | 2021.08.03 |

| ADC - 성능지표 (0) | 2021.06.25 |