본 문서는 TI사의 https://www.ti.com/lit/pdf/snla415 문서를 정리한 것입니다.

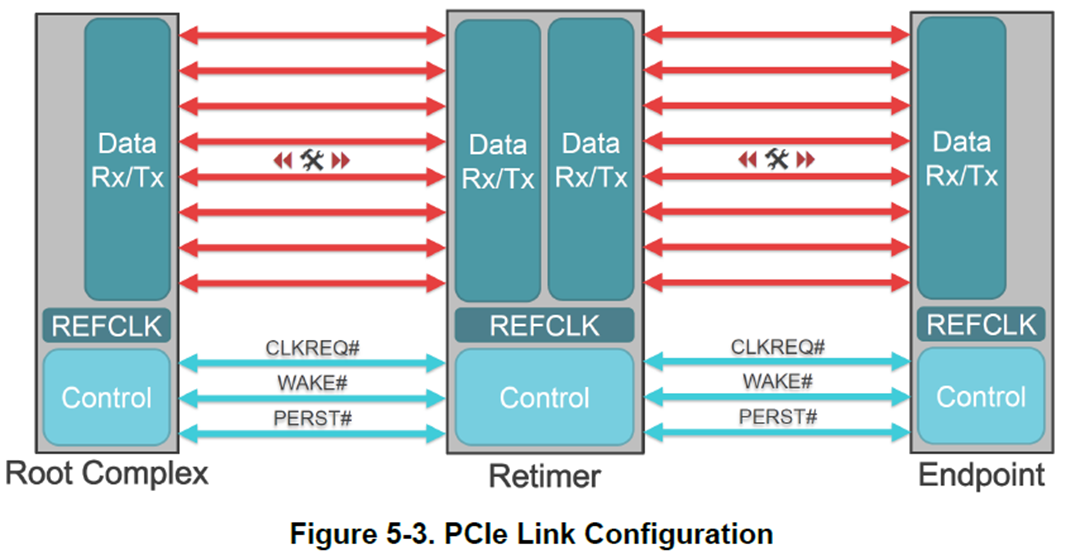

3. Components of PCIe Communication

3.1 Root Complex

Root Complex는 CPU, 메모리, PCIe 장치 사이를 연결한다. Root Complex는 CPU 내부에 있는 경우도 있고, 외부에 있는 경우도 있다.

PCIe endpoint가 출력하는 데이터가 CPU, 메모리에 전달되려면 Root Complex를 거쳐야 한다.

1개의 Root Complex와 다수의 PCIe endpoint 간에 PCIe 통신이 이루어진다.

3.2 Repeater

Repeater는 Root complex와 PCIe endpoint 간에 거리가 멀거나, 선로의 신호 전달 품질이 좋지 않은 경우, Pcie 통신이 원활하게 이루어지도록

한다. 이것을 영어로 Signal conditioning이라고 한다. Repeater는 2가지 종류가 있다. retimer, redriver이다.

3.3 Endpoint

보통 우리가 사용하는 PCIe 장치들인 GPU, SSD(M.2 Solid state drive)는 PCIe통신에서는 endpoint이다.

※ PCIe Endpoint와 PCI Endpoint는 다른 것이다. 요즘 24년도에는 PCI 장치는 보기 어렵다.

대략적으로 PCI Endpoint는 Parallel 방식 통신이며, PCIe는 Serial 방식 통신이다.

4. Signaling

PCIe 장치(Root Complex, Endpoint 등)들은 PERST#, WAKE, CLKREQ, REFCLK 신호를 이용하여 PCIe 통신을 시작한다.

4.1 PERST > 일명 Reset 신호

PCIe 장치가 장착된 시스템에 전원이 켜졌을 때, 공급전압과 REF CLK가 안정화 될때까지 PERST 신호를 LOW로 유지하여 PCIE 장치를 리셋

상태로 유지한다. PERST 신호가 LOW > High 될 때, PCIe endpoint와 Root Complex 간 Link Training을 시작한다.

4.3 REFCLK

PCIe 장치들은 통신 시작 전 반드시 REF CLK를 안정적으로 받는 상태여야 한다.

이 문서에서 말하는 PCIe 장치는 End point만 지칭하는 것이 아니다. PCIe 통신에 참여하는 Root Complex, Repeater도 포함시킨다.

5. Link training

Signaling 신호가 갖추어진 상태라면 PCIe 장치들은 Link training은 RX detect, Polling, configuration으로 구성된다. 이 과정을 PCIe endpoint는 Root Complex가 연결 완료된다.

5.1 Receiver Detect (Rx Detect)

REF CLK, 전원이 갖추어진 상태이면 PCIe 장치들은 각 lane마다 배정된 RX Detect 회로를 이용하여, PCIe 통신을 할 수 있는 상대가 각 lane마다 있는지 확인한다.

5.2 Polling

RX detect 단계가 끝나면 PCIe 장치들은 PCIe gen 1.0(2.5Gbps) 속도로 training sequence를 서로 전송한다. 이 과정을 통해 Bit lock, Symbol lock을 확인한다.

Bit lock : 수신측이 송신측의 Clock에 동기화 할 수 있음을 알려줌.

Symbol lock : 수신측이 송신측에서 보낸 10bit 심볼을 decode할 수 있음을 알려줌

※ 수신측 장치는 endpoint만을 의미하지 않는다. PCIe 통신의 송수신은 end point 말고도, root complex, repeater 모두 송신, 수신을 한다.

5.3 Configuration

이 과정은 lane과 lane 사이에 발생할 수 있는 skew를 없애는 작업이다. Configuration 과정을 통해 PCIe 통신이 가능한 Lane의 개수와 link 번호가 결정된다.

PCIe Gen1 속도만 지원하는 PCIe 장치라면, Link training이 끝나고 L0 state로 넘어간다.

L0 state에서는 Root complex와 Endpoint가 서로 데이터를 송수신 할 수 있게 된다.

※ skew는 여러 개의 lane이 있을 때, lane마다 길이가 다를 수 있기 때문에 생긴다.

6. Link Equalization

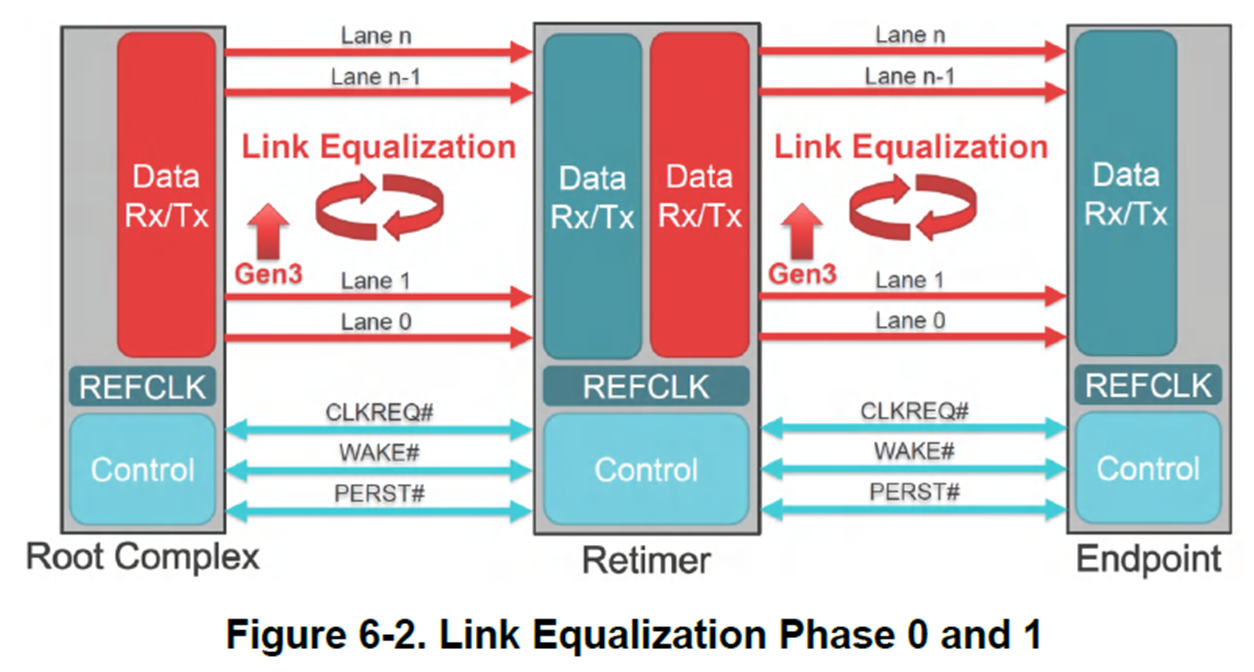

PCIe 장치가 Gen3 속도 이상을 지원하는 경우 Link training 과정이 끝나고 Link equalization 과정이 진행된다.

Link equalization은 PCIe 장치가 지원하는 속도에 따라 여러 번 진행 될 수 있다. 예를 들어 Gen 5 속도를 지원하는 PCIe 장치의 경우 3번의 Link equalization이 진행된다. Gen 1 > Gen3, Gen3 > Gen4, Gen 4> Gen 5

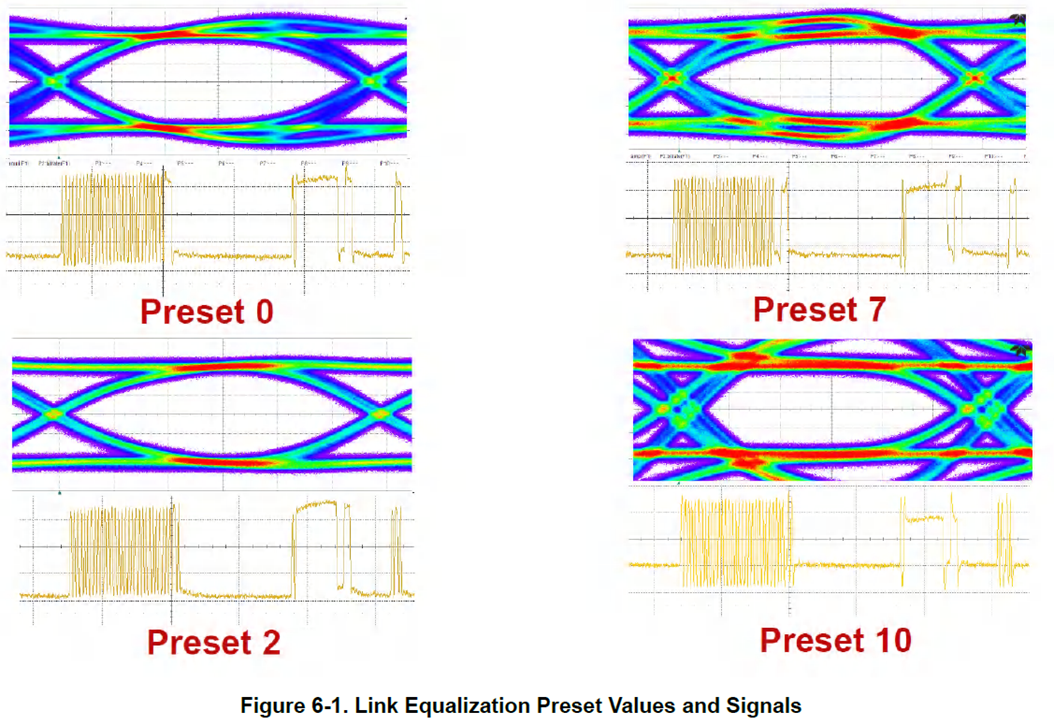

Link equalization 과정의 특징으로 preset value라는 값을 변경하면서, 신호의 전달 특성을 평가하고 신호의 전송 품질을 변경할 수 있다는 점이다. Gen3, Gen4의 경우 11가지의 Preset value값들이 정해져 있다.

PCIe 장치들이 신호의 품질을 평가하기 위해, preset value값을 변경하며 송신한다. 그리고 신호의 전달 특성을 각각 평가한다. 신호의 특성이 가장 좋았던 preset value값이 PCIe 통신에 사용된다.

Link equalization은 Phase0,1,2,3 4가지 단계로 구성된다.

다음 그림은 Preset value값을 변경하면서 신호의 특성을 eye diagram으로 측정한 것이다.

6.1 phase 0 and 1

Phase 0 : root complex와 endpoint는 연결된 lane마다 preset value, training sequence를 주고 받는다. 이 때 Gen 3 속도 규격으로 주고 받는 것이 통과되면 Phase0에서 Phase1으로 넘어간다.

Phase1 : phase 0에서 했던 과정을 반복하여 진행한다. BER이 10^-4 보다 작아질 때까지 진행한다.

이 과정이 통과되면 Phase 2,3이 진행된다.

6.1 phase2 and 3

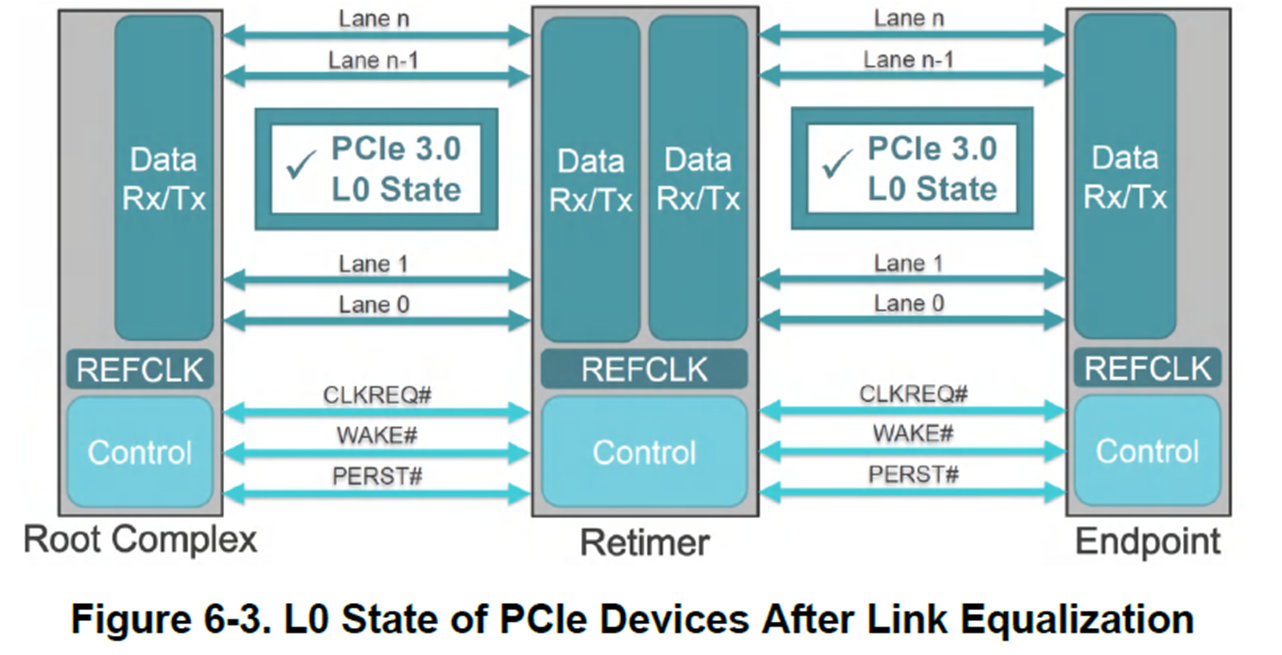

Phase 2: Upstream 기기에서 Downstream 기기방향으로 Preset value를 변경하면서 link equalization을 수행한다. BER이 10^-12보다 작은 경우 Equalization 과정이 끝나고 L0 state로 넘어간다.

Phase 3: Downstream 기기에서 upstream 기기 방향으로 Phase2과정을 수행한다.

※ 문서상에서 upstream 기기는 Root Complex, Downstream 기기는 endpoint 로 보임.

L0 state : PCIe Gen3 속도에서 신뢰성 있게 데이터를 송수신할 수 있다는 것을 보증한다.

PCIe Gen 4,5 까지 가기 위해서는 Link equalization 과정을 2번 더 거쳐야 한다.

7. Summary

Link training : root complex와 endpoint를 연결하는 과정, 이 과정이 완료되면 Gen1 속도로 PCIe 통신이 가능

Link equalization : PCIe 장치들이 Gen3를 지원하는 경우에는 Link training이 끝나고 Link equalization 과정이

진행된다. Gen1보다 더 빠른 속도로 PCIe 통신이 가능한지 확인하는 작업이다.

이 과정을 통과하면 PCIe 장치들은 BER(Bit Error Rate)이 10^-12 아래인 상태에서 데이터를 주고 받을 수 있다

'FPGA - 프로세서 그리고 데이터의 이동 > PCIe' 카테고리의 다른 글

| PCIe 장치 인식 과정 (0) | 2024.07.31 |

|---|---|

| PCIe slot에 꽂힌 FPGA 카드를 CPU가 인식하는 과정 (0) | 2024.03.11 |

| FPGA의 PCIe에 접근에 필요한 file descriptor는 무엇인가? (1) | 2024.02.05 |

| PCIe - lspci , link status (0) | 2021.11.23 |

| PCIe 통신 - Configuration Space, Base Address Register 개념 (2) | 2021.07.23 |